1、锁相环的基本组成

锁相环路是一种负反馈控制电路(Phase-Locked Loop 相位锁定环路),简称PLL。特点是:利用外部输入的参考信号控制环路内部震荡信号的频率和相位。

因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。

在锁相环路工作时,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差,即输出电压与输入电压的相位被固定住(锁住),这就是锁相环名称的由来。

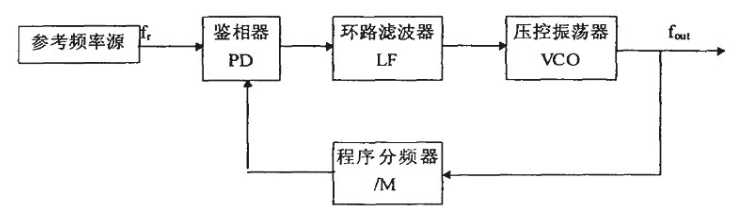

锁相环通常由鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)三部分组成

锁相环(PLL)组成原理框图

在这个图里,锁相环中的鉴相器又称为相位比较器。

它的作用是检测输入信号和输出信号的相位差,并将检测出的相位差信号转换成 uD(t) 电压信号输出。

该信号经低通滤波器滤波后形成压控振荡器的控制电压 uC(t) ,对振荡器输出信号的频率实施控制。

2、锁相环的工作原理

锁相环的工作原理分为以下几个步骤:

(1)当输入信号与反馈信号的相位不同步时,相位比较器(PD)检测到相位差,并生成一个与相位差成正比的电压信号。

(2)滤波器(LF)对电压信号进行滤波,去除噪声和抖动。

(3)电压控制振荡器(VCO)根据滤波后的电压信号调整输出信号的频率和相位,使输出信号逐渐接近输入信号的相位。

(4)当输出信号与输入信号的相位达到同步时,锁相环进入锁定状态,系统维持稳定度相位同步。

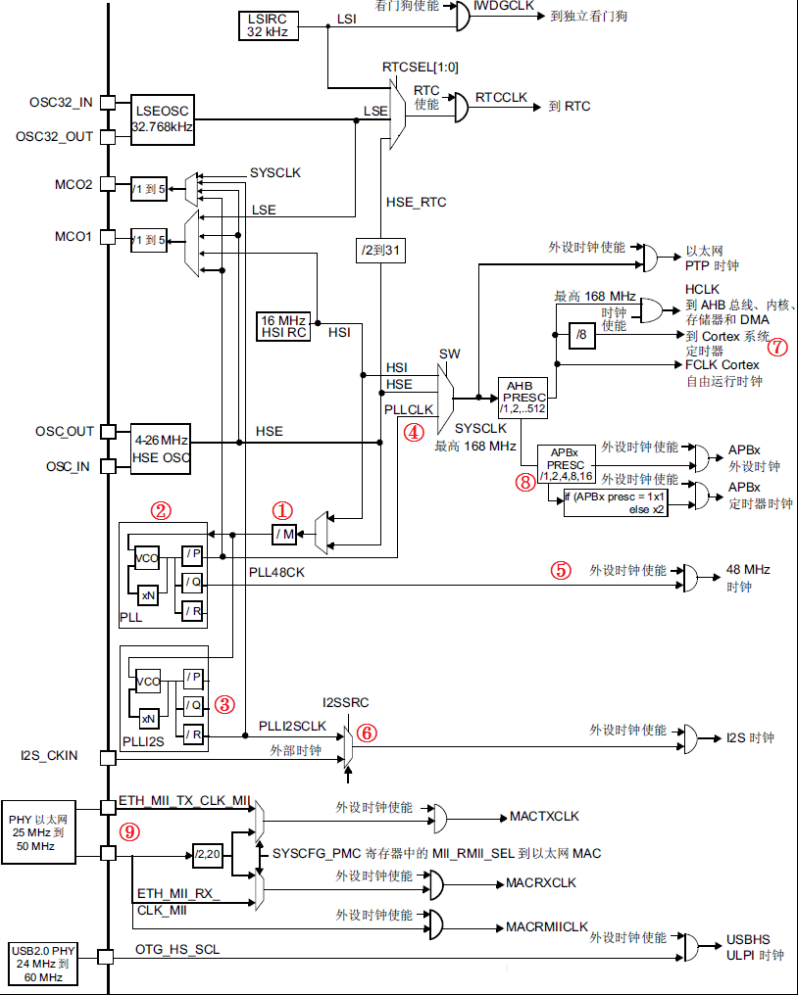

3、STM32中锁相环的应用

在STM32中,锁相环主要有以下作用:

- 1、系统时钟生成:STM32通常用锁相环从外部晶震或者内部时钟源生成所需的系统时钟。例如:通过使用PLL,可以将外部8MHz晶振提升到72MHz或者更高,以满足高性能应用的需求。

- 2、USB时钟生成:在具有USB功能的STM32微控制器中,锁相环可以用于生成精确的48MHz时钟,满足USB 2.0全速(12Mbps)或高速(480Mbps)通信的需求。

- 3、音频时钟生成:在音频处理器应用中,STM32的PLL可以用于生成特定的硬盘采样率(44.1kHz,48kHz等)以及I2S和SPDIF接口所需的位时钟和帧时钟。

- 4、ADC和DAC时钟生成:在高速数据采集和信号处理应用中,PLL可以用于为ADC和DAC提供精确的采样时钟,从而实现高性能的数据转换。

4、总结

锁相环在通信和电子领域有广泛的应用,它为实现高精度时钟信号提供了重要支持,本文简单介绍了锁相环基本原理,工作方式和应用。

参考文献:

【STM32】知识补充 锁相环原理与应用解析_stm32数字锁相-CSDN博客

STM32F4开发指南-寄存器版本(正点原子)

I used to be very happy to seek out this internet-site.I needed to thanks on your time for this wonderful learn!! I positively enjoying every little little bit of it and I’ve you bookmarked to check out new stuff you blog post.